Подложка IC используется для инкапсулирования голых пластинок интегральных схем (IC), характеризующихся высокой плотностью, высокой точностью, высокой производительностью, миниатюризацией и тонкостью и т.д. Он используется для формирования чипа вместе с трубкой и свинцовыми проводами после инкапсуляции и испытания. Основная роль включает в себя перевозку пластин, обеспечение рассеивания тепла, защиту и фиксацию чипа, а также одновременно между чипом и PCB для обеспечения электронного соединения. В целом, подложка IC играет роль в поддержке чипа, но также играет роль в электрическом соединении.

Технические характеристики подложек IC включают миниатюризацию, высокую плотность, многофункциональность, низкое энергопотребление и высокую надежность. Требование к текущей диафрагме микровии достигает от 50 до 100 микронов с шириной линии от 20 до 50 микронов.

Подложки IC часто могут быть классифицированы на основе материала, структуры и функции. Ее основные типы включают в себя:- Жесткая упаковка подложка: в основном изготовлена из эпоксидной смолы, BT смолы или ABF смолы, которая является наиболее широко используемой- Гибкие упаковки подложки: обычно изготовлены с полиимидной (PI) или полиэстер (PE) смолы, подходящие для сценариев применения, которые требуют гибкости и тонкости-Керамические упаковки подложки: Составлены из керамических материалов, таких как алюминий, нитрид алюминия или карбид кремния, они обеспечивают лучшее тепловое стабильность

Подложки ICшироко используются в мобильной связи, автомобильной электронике и потребительской электронике. Например, в устройствах связи 5G подложки IC должны не только

поддерживать высокочастотную передачу сигнала, но и иметь хорошую производительность рассеивания тепла, чтобы удовлетворить спрос на высокую производительность в умных

устройствах. С быстрым развитием рынков IoT и умных устройств рыночный спрос на субстраты IC продолжает расти.

Производство подложек IC сталкивается с множеством ограничений, включая технические барьеры, выбор материалов, сложность производственного процесса и быстрые изменения

спроса на рынке. Производство IC-субстратов технически очень требовательно, включает сложные производственные процессы и сложное производственное оборудование. Наличие

технических барьеров затрудняет выход некоторых малых предприятий на рынок, что еще больше усугубляет дисбаланс конкуренции в отрасли. Процесс изготовления IC-субстратов

очень сложный и требует высокого уровня технической поддержки. Каждый этап производственного процесса должен обеспечивать высокую точность, высокую плотность и стабильность.

Эти факторы влияют на производительность и стоимость IC-субстратов.

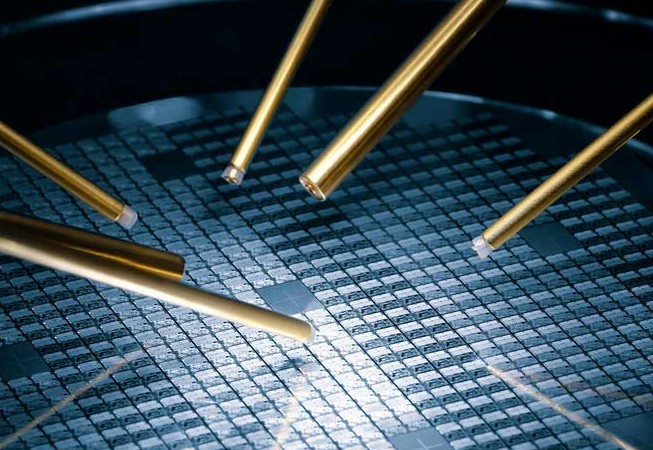

Помимо производства подложек IC, это также включает в себя очень важную технологию производства - технологию связывания IC и пластин, на основе которой могут быть объединены подложки IC и пластины и реализованы электрические характеристики продукта.

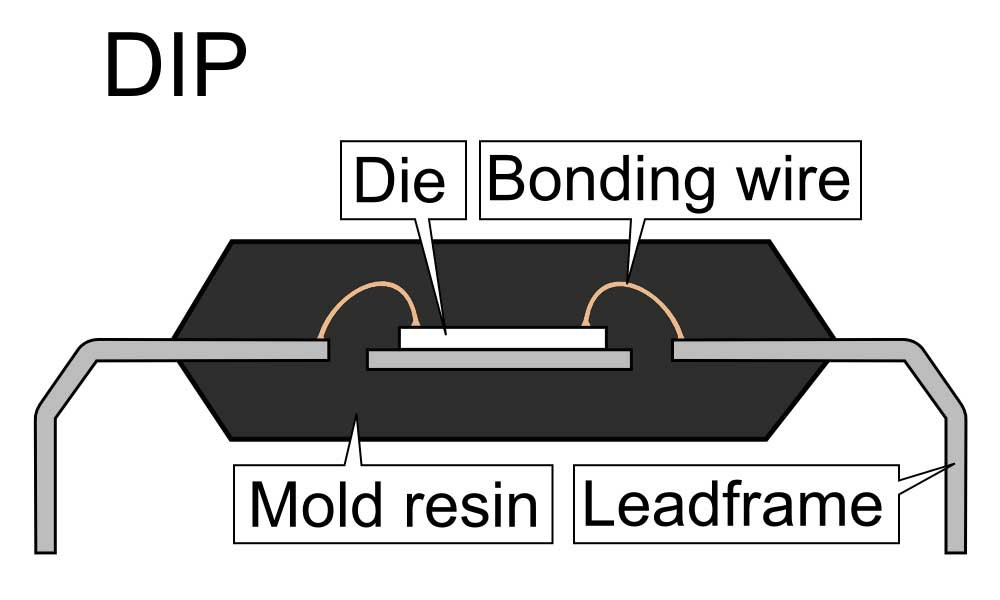

Технология соединения IC в основном относится к процессу электрического соединения чипа IC к плате-носителю во время процесса упаковки полупроводников. Технологии связывания включают COB (Chip-on-Board) и Flip Chip, которые обеспечивают эффективные электрические соединения между подключенными чипами и субстратом.

- Чип на борту (COB): технология мягкой упаковки IC, упаковка голых чипов или приклеивание (приклеивание), то есть чип приклеивается непосредственно к плате схем, чтобы достичь косвенного соединения, сведенного к минимуму. Эта технология может значительно уменьшить размер пакета и улучшить общую интеграцию и производительность.

- Flip Chip: чип перевернут на его передней стороне, и удары непосредственно подключены к доске-носителю в форме упаковки. В этой технологии точка контакта чипа расположена в его нижней части и подключена к доске-носителю через небольшие паевые удары.