2.5D packaging and 3D IC packaging also differ in application scenarios and performance. 2.5D encapsulation is commonly used in high-performance computing, network communication, artificial intelligence, mobile devices, and other fields, with high performance and flexible design; 3D IC packaging is usually applied in fields such as memory, sensors, medical devices, etc., with high integration and small packaging volume.

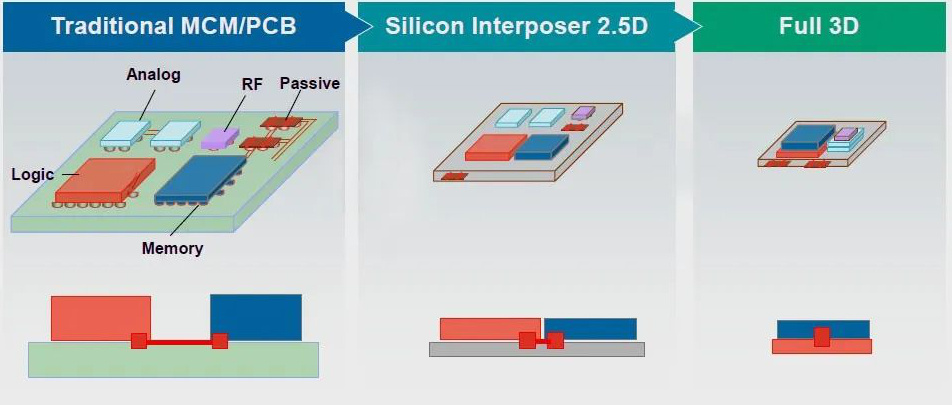

2.5D and 3D semiconductor packaging technologies are crucial for the performance of electronic devices. Both solutions have enhanced performance, reduced size, and improved energy efficiency to varying degrees. 2.5D packaging is beneficial for combining various components and reducing footprint. It is suitable for applications in high-performance computing and artificial intelligence accelerators. The principle of 3D packaging is to create transistor structures on chips and directly use silicon through holes to connect electronic signals from different chips, allowing for vertical stacking of memory or other chips on top. 3D packaging provides unparalleled integration, efficient heat dissipation, and shortened interconnect length, making it an ideal choice for high-performance applications. In the fast-paced semiconductor technology field, packaging plays a crucial role in determining the performance, size, and power efficiency of electronic devices. The two famous packaging technologies, 2.5D and 3D packaging, have become outstanding solutions. Each technology has unique advantages and challenges, which are factors that semiconductor manufacturers and designers must consider. We will explore the differences and applications between 2.5D and 3D packaging.

Упаковка в формате 2.5D и 3D

Разбирайтесь в упаковке в формате 2.5D

нкапсуляция 2.5D, также известная как технология промежуточного слоя 2.5D, является промежуточным этапом между традиционной 2D-инкапсуляцией и зрелой 3D-инкапсуляцией. В корпусе 2.5D несколько полупроводниковых чипов, использующих различные технологические процессы, обычно размещаются бок о бок на промежуточном кремниевом слое. Промежуточный слой действует как мост, соединяющий различные чипы и обеспечивающий высокоскоростные интерфейсы связи. Такое расположение обеспечивает большую гибкость при объединении различных функций в одном корпусе. Наиболее популярная технология интеграции в формате 2.5D предполагает объединение кремниевого промежуточного слоя с TSV. В этой конфигурации чип обычно подключается к промежуточному слою с использованием технологии MicroBump. Кремниевая подложка, используемая в качестве интерполятора, подключается к подложке с помощью рельефных соединений. Поверхности кремниевой подложки соединены между собой с помощью распределительного слоя (RDL), в то время как TSV служат каналами для электрических соединений между верхней и нижней поверхностями кремниевой подложки. Интеграция кремния с TSV является наиболее распространенной технологией интеграции в формате 2.5D. Микросхема обычно соединяется с промежуточным слоем через микроудары, а кремниевая подложка в качестве промежуточного слоя соединяется с подложкой через выступы. Поверхность кремниевой подложки соединена проволокой RDL, а TSV служит каналом электрического соединения между верхней и нижней поверхностями кремниевой подложки. Такая интеграция в формате 2.5D подходит для ситуаций, когда размер чипа относительно велик, а плотность выводов высока. Как правило, чип устанавливается на кремниевую подложку в виде флип-чипа. Такая интегрированная форма 2.5D очень подходит для сценариев с большими размерами чипов и высокими требованиями к плотности выводов. Обычно чипы монтируются на кремниевую подложку в конфигурации флип-чип.

Разбирайтесь в упаковке 2.5D

Инкапсуляция 2.5D, также известная как технология промежуточного слоя 2.5D, является промежуточным этапом между традиционной 2D-инкапсуляцией и зрелой 3D-инкапсуляцией. В корпусе 2.5D несколько полупроводниковых чипов, использующих различные технологические процессы, обычно размещаются бок о бок на кремниевом промежуточном слое. Промежуточный слой действует как мост, соединяющий различные чипы и обеспечивающий высокоскоростные интерфейсы связи. Такое расположение обеспечивает большую гибкость при объединении различных функций в одном корпусе. Наиболее популярная технология интеграции в формате 2.5D предполагает объединение кремниевого промежуточного слоя с TSV. В этой конфигурации чип обычно подключается к промежуточному слою с использованием технологии MicroBump. Кремниевая подложка, используемая в качестве интерполятора, подключается к подложке с помощью рельефных соединений. Поверхности кремниевой подложки соединены между собой с помощью распределительного слоя (RDL), в то время как TSV служат каналами для электрических соединений между верхней и нижней поверхностями кремниевой подложки. Интеграция кремния с TSV является наиболее распространенной технологией интеграции в формате 2.5D. Микросхема обычно соединяется с промежуточным слоем через микроудары, а кремниевая подложка в качестве промежуточного слоя соединяется с подложкой через выступы. Поверхность кремниевой подложки соединена проволокой RDL, а TSV служит каналом электрического соединения между верхней и нижней поверхностями кремниевой подложки. Такая интеграция в формате 2.5D подходит для ситуаций, когда размер чипа относительно велик, а плотность выводов высока. Как правило, чип устанавливается на кремниевую подложку в виде флип-чипа. Такая 2,5-мерная интегрированная форма очень подходит для сценариев с большими размерами чипов и высокими требованиями к плотности выводов. Обычно чипы монтируются на кремниевую подложку в конфигурации с флип-чипом.

Преимущества упаковки в формате 2.5D

Повышенная производительность: Пакет 2.5D позволяет интегрировать несколько компонентов, таких как процессоры, память и датчики, в единый пакет. Такая близость приводит к укороченному соединению

длина, тем самым улучшая целостность сигнала и уменьшая задержку. Уменьшение размера: Благодаря укладке чипсов на промежуточный слой упаковка формата 2,5 D уменьшает общую площадь упаковки.

(по сравнению с 2D), что делает его идеальным выбором для небольших и тонких устройств. Повышение энергоэффективности: Более короткие межсоединения и оптимизированная компоновка микросхем в корпусе 2.5D позволяют снизить энергопотребление.

потребление, что делает его подходящим для устройств, работающих на батарейках.

Применение 2.5-мерной упаковки

2.5-мерная упаковка применяется в различных отраслях промышленности, включая высокопроизводительные вычисления, центры обработки данных и сетевое оборудование. Она особенно подходит для систем искусственного интеллекта (ИИ)

ускорителей, где требуется эффективная совместная работа нескольких типов микросхем.

Разбираемся в 3D-упаковке

3D-упаковка выводит интеграцию на новый уровень, объединяя несколько полупроводниковых чипов в трехмерную структуру. Этот метод повышает общую производительность и функциональность упаковки. Это приводит к уменьшению длины межсоединений и размеров упаковки. Однако по мере того, как чипы осваиваются в области 3D-микросхем (где логические микросхемы или микросхемы памяти устанавливаются друг на друга), процессы проектирования, производства, получения конечного продукта и тестирования становятся все более сложными. В области 3D-упаковки существует множество методов для удовлетворения различных требований. Существует "настоящая 3D" упаковка, в которой пластины сложным образом укладываются друг на друга для достижения максимальной интеграции. Существует еще один тип "интеграции 3D-систем на кристалле (SoC)", который может включать в себя такие функции, как наложение слоев распределения питания на задней панели или пластин памяти друг на друга. Наконец, "3D-система в упаковке (SiP)" предполагает расстояние между контактами около 700 микрон и использование упаковки на уровне пластин. Каждый из этих методов отвечает конкретным техническим требованиям и задачам в области 3D-упаковки.

Преимущества 3D-упаковки

Беспрецедентная интеграция: 3D-упаковка обеспечивает максимально компактную интеграцию различных компонентов и функций, позволяя создавать сложные системы с компактным форм-фактором.

Улучшение теплоотдачи: Вертикальное расположение чипов в 3D-упаковке позволяет добиться эффективного теплоотвода и решить тепловые проблемы, связанные с высокопроизводительными вычислениями.

Сокращение длины межсоединений: 3D-упаковка дополнительно сокращает длину межсоединений (более 2,5D), тем самым максимально сокращая задержку сигнала и энергопотребление. A

значительным преимуществом технологии 3D-упаковки является сокращение расстояния между элементами. В многослойной 3D-конструкции расстояние между компонентами примерно в 0,7 раза больше, чем в 2D-конструкции.

структура. Уменьшение этого расстояния напрямую влияет на энергопотребление соединительной части системы, поскольку приводит к уменьшению емкости. Таким образом, текущее энергопотребление составляет

примерно в 0,7 раза больше, чем в 2D-конфигурациях.

Применение в 3D-упаковке

3D-упаковка в основном применяется при сборке однотипных микросхем, когда несколько идентичных микросхем вертикально укладываются друг на друга и соединяются между собой с помощью TSV, проходящих через пакет микросхем.

3D-упаковка становится все более популярной в приложениях, где решающее значение имеют высокая производительность и миниатюризация. Он обычно используется для передовых технологий запоминания, таких как высокая

широкополосная память (HBM) и передовые процессоры для смартфонов высокого класса, игровых консолей и профессиональных компьютеров.