Подложка микросхемы в основном используется для размещения микросхем (интегральных схем) с внутренней проводкой для передачи сигналов между микросхемами и печатными платами. Помимо своей несущей функции, микросхемная подложка также выполняет дополнительные функции, такие как защита цепей и выделенных линий, проектирование путей отвода тепла и установление модульных стандартов для компонентов.

Микросхемы разрабатываются на основе печатных плат HDI, и между ними существует определенная корреляция. Однако технологический порог для микросхемных подложек намного выше, чем для печатных плат HDI и обычных печатных плат PCB. Под микросхемными подложками можно понимать высококачественные печатные платы, которые обладают такими характеристиками, как высокая плотность, высокая точность, большое количество контактов, высокая производительность, миниатюризация и тонкость. Для них требуются более высокие технические параметры, особенно параметры ширины основной линии/межстрочного интервала.

Подложка микросхемы является ключевым материалом для упаковки транзисторов. Производство интегральных схем состоит из трех этапов: разработка микросхем, изготовление пластин и тестирование упаковки. Упаковка не только служит для защиты чипа и повышения теплопроводности, но и соединяет внешние цепи с внутренней частью чипа для выполнения функции фиксации чипа. Подложка для упаковки микросхем (IC Package Substrate, также известная как Package Substrate) является ключевым элементом в процессе тестирования упаковки и используется для установления сигнальных соединений между микросхемами и печатными платами. Микросхемные подложки также могут играть важную роль в защите цепей, их закреплении и отводе избыточного тепла.

Микросхемные подложки применяются в основных технологиях упаковки. Упаковка транзисторных микросхем претерпела несколько изменений в зависимости от технологии упаковки: DIP-упаковка (технология двойной встроенной упаковки), SOP-упаковка (упаковка малого форм-фактора), QFP-упаковка (упаковка в виде небольшой квадратной плоскости), PGA-упаковка (технология упаковки с контактной сеткой), BGA-упаковка (упаковка в виде шариков припоя упаковка) и SIP-упаковка (упаковка на системном уровне). Развитие и модернизация технологии позволили увеличить площадь упаковки и чипсов до 1.

Если взять в качестве примера упаковку BGA (Ball grid array), то это технология упаковки с высокой плотностью, которая отличает ее от других упаковочных чипов, расположенных вокруг чипа. Контакты BGA расположены на нижней поверхности упаковки, что увеличивает расстояние между клеммами ввода-вывода и количество подключаемых устройств ввода-вывода. BGA-упаковка стала одной из основных технологий упаковки благодаря своей высокой производительности, хорошим электрическим характеристикам и пригодности для высокочастотных цепей. На основе BGA постепенно появились конвейеры для упаковки микросхем высокой плотности, такие как CSP, MCM и SIP. Передовые технологии упаковки в большей степени соответствуют характеристикам миниатюризации, сложности и интеграции интегральных схем. Микросхемные подложки широко используются в основных упаковочных технологиях благодаря их высокой точности, высокой плотности, миниатюризации и тонкости.

Существуют различные типы микросхемных подложек, и они широко используются. Их можно классифицировать в зависимости от конвейера для упаковки, материала для обработки и области применения.

1. В соответствии с классификацией упаковочных трубопроводов, подложки IC подразделяются на подложки для упаковки BGA, подложки для упаковки CSP, подложки для упаковки FC и подложки для упаковки MCM.

2. В соответствии с классификацией упаковочных материалов подложки IC делятся на твердые упаковочные подложки, гибкие упаковочные подложки и керамические упаковочные подложки. Жесткая упаковочная основа в основном изготовлена из смолы BT или ABF с коэффициентом теплового расширения (CTE) приблизительно от 13 до 17 частей на миллион/°C. Гибкая упаковочная основа в основном изготовлена из смолы PI или PE с коэффициентом теплового расширения (CTE) приблизительно от 13 до 27 частей на миллион/°C. Керамические подложки для упаковки в основном изготавливаются из керамических материалов, таких как оксид алюминия, нитрид алюминия или карбид кремния, которые имеют относительно низкий CTE, около 6-8 частей на миллион/°C.

3. В соответствии с классификацией областей применения подложки микросхем делятся на подложки для упаковки микросхем памяти, подложки для упаковки микроэлектромеханических систем, подложки для упаковки радиочастотных модулей, подложки для упаковки процессорных микросхем и подложки для упаковки высокоскоростных коммуникационных систем.

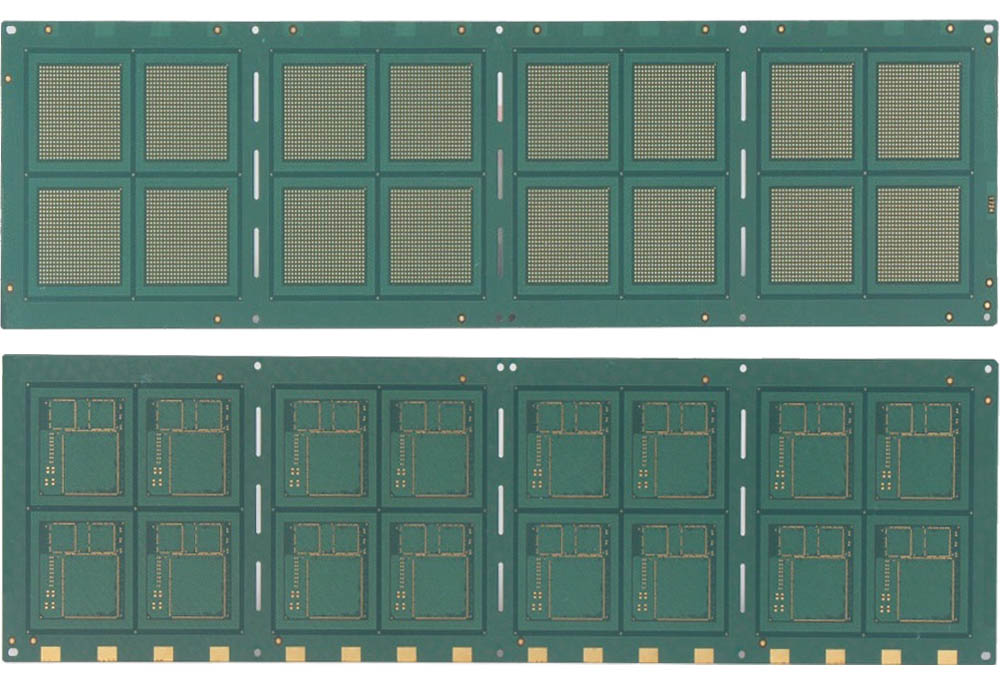

Подложка для упаковки BGA

Требования, предъявляемые к IC-подложкам с точки зрения параметров, намного выше, чем к обычным печатным платам и HDD-диодам. В зависимости от ширины строки/межстрочного интервала обычные изделия на IC-подложках могут достигать 20 мкм/20 мкм2. Ширина строк/интервал между строками на высококачественных микросхемах будет уменьшена до 10 мкм/10 мкм. 5 мкм/5 мкм. А для обычных печатных плат ширина строк/интервал между строками составляет 50 мкм/50 мкм выше метра.

Существует два типа процессов изготовления подложек для микросхем, а именно SAP (полуаддитивный метод) и MSAP (улучшенный полуаддитивный метод), которые используются для производства изделий шириной линии/межстрочного интервала менее 25 мкм. Изделия с более сложным технологическим процессом. Производственные принципы SAP и MSAP схожи и вкратце описываются как нанесение тонкого слоя меди на подложку с последующим графическим оформлением, нанесение гальванического слоя меди требуемой толщины и, наконец, удаление начального слоя меди. Основное различие между этими двумя технологическими процессами заключается в толщине слоя затравочной меди. Процесс SAP начинается с нанесения тонкого слоя химически обработанной меди (менее 1,5 мкм), в то время как MSAP начинается с нанесения тонкого слоя ламинированной медной фольги (более 1,5 мкм).

Субтрактивный метод - это метод изготовления печатных плат, который вкратце описывается как нанесение гальванического слоя меди на всю поверхность покрытой медью платы, защита схемы и сквозных отверстий, вытравливание ненужных медных листов и оставление меди в схеме и сквозных отверстиях. Наиболее очевидным недостатком метода восстановления является его высокая боковая коррозия, что означает, что слой меди также будет вытравливаться сбоку в процессе нисходящего травления, что ограничивает точность метода восстановления. Таким образом, минимальная ширина линии/интервал между строками при методе вычитания может достигать только 50 мкм. Если ширина линии/интервал между строками<50 мкм и выход слишком низкий, метод вычитания использовать нельзя.

В процессе производства подложек для микросхем существует множество технологических трудностей, которые отражаются в пяти аспектах: контроль расширения и сжатия материала, формирование графических изображений, меднение, нанесение паяльной маски и обработка поверхности на протяжении всего процесса.