1. Основы упаковки транзисторов

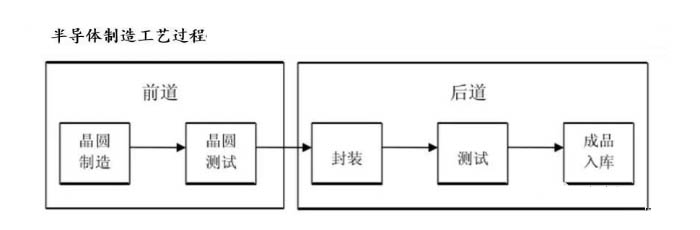

Производство транзисторов включает в себя изготовление пластин, их тестирование (проба/ сортировка), упаковку (сборку), тестирование и, наконец, складирование готовой продукции.

Технологический процесс изготовления транзисторов

1.3. Инкапсулированные функции

Самой основной функцией упаковки является защита микросхемы от воздействия окружающей среды (включая физические и химические воздействия). Поэтому в первоначальной микроэлектронной упаковке металлическая банка использовалась в качестве оболочки для герметичной защиты хрупких электронных компонентов, которые были полностью изолированы от внешнего мира. Однако с развитием технологий производства интегральных схем, особенно с постоянным совершенствованием процесса изготовления пассивирующего слоя на пластинах, функции упаковки постепенно вытесняются.

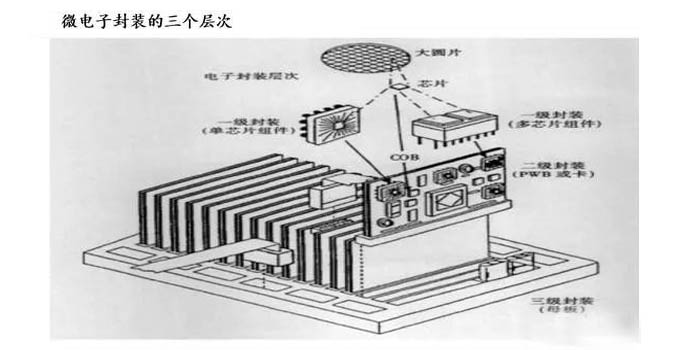

Три уровня микроэлектронной упаковки

Электронная упаковка включает в себя сложные системы с использованием различных материалов и технологических процессов, классифицируемые по геометрическим размерам, таким как "точка, линия, поверхность, корпус, блок и плата". Электронные подложки служат основой для упаковки транзисторных чипов, поддерживая электронные компоненты, такие как печатные платы и модульные подложки. Появление ламинированных многослойных плат расширило возможности использования подложек. Упаковочные подложки (PKG-субстраты), такие как BGA, CSP, TAB и MCM, представляют собой новые модульные подложки, устанавливаемые на печатные платы и поддерживающие различные форматы упаковки. Эти подложки не только поддерживают микросхемы и компоненты, но и лежат в основе целых систем электронных схем, что требует усовершенствования многослойных подложек высокой плотности для улучшения функциональности и производительности при разработке электронных упаковочных материалов.

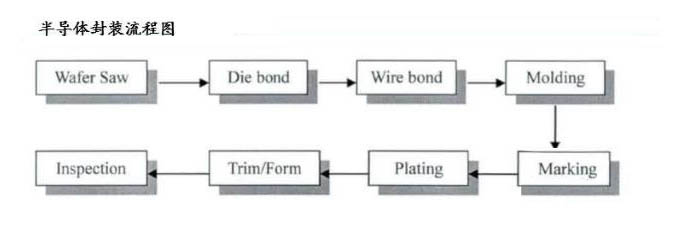

Процесс упаковки транзисторов

Суть технологии упаковки микросхем заключается в обеспечении стабильной защитной среды для микросхем интегральных схем при одновременном установлении эффективного соединения с внешними микросхемами. Процесс упаковки включает в себя такие этапы, как нарезка микросхем, подключение выводов и формирование оболочки упаковки. Он предназначен для защиты микросхемы от воздействия внешней среды и обеспечения передачи сигнала между цепями с низким уровнем шума и малой задержкой. С развитием технологий технология упаковки постоянно оптимизируется, уменьшается размер чипа, увеличивается плотность контактов, а также повышается термостойкость и надежность.

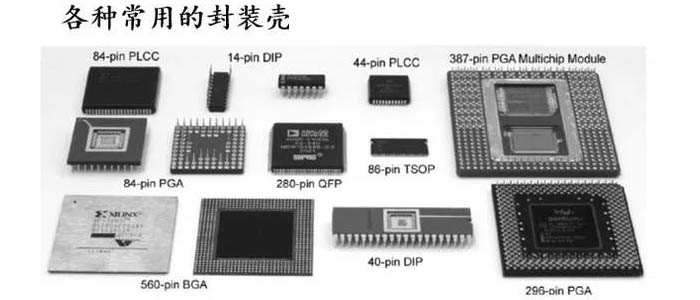

Часто используемые пакеты

Историю развития технологии упаковки транзисторов можно разделить на три этапа:

1. Первый этап (до 1970-х годов): в основном это были вставные упаковки со сквозными отверстиями, такие как металлическая круглая упаковка (TO type) и керамическая двойная встраиваемая упаковка (CDIP), среди которых пластиковая двойная встраиваемая упаковка (PDIP) стала основным продуктом.

2. Второй этап (после 1980-х годов): внедрение упаковок для поверхностного монтажа, таких как пластиковая упаковка для вырезания свинцовых чипов (PLCC) и пластиковая четырехслойная плоская упаковка (PQFP), способствовало развитию форм упаковки для повышения плотности и эффективности.

3. Третий этап (после 1990-х годов): размер транзисторов достиг сверхмасштабной интеграции, и линейка выводов изменилась с плоских четырехпроводных на плоские шариковые решетки (BGA), что способствовало появлению новых технологий упаковки, таких как упаковка на уровне чипа (CSP) и удовлетворяют требованиям миниатюризации и высокой производительности.

В целом, технология упаковки транзисторов продолжает развиваться по мере развития электронных устройств - от традиционной упаковки с разъемами до современной упаковки для поверхностного монтажа и упаковки с шариковыми решетками, постоянно повышая плотность упаковки, эффективность и функциональность.

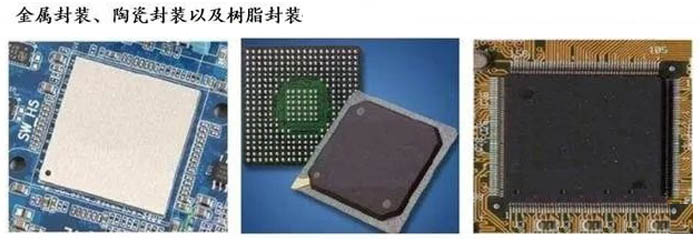

Металлическая упаковка, керамическая упаковка (C), пластиковая упаковка (P)

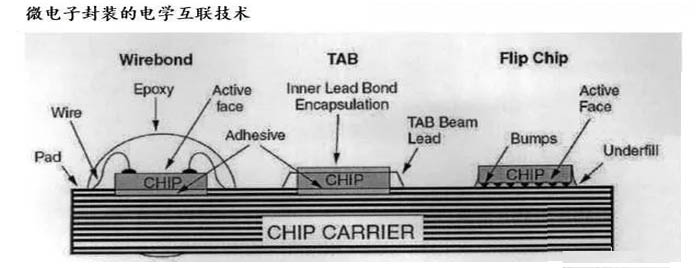

В микроэлектронной упаковке электрическое соединение микросхем является ключевым звеном, обеспечивающим надежность устройства. Основные методы соединения включают в себя соединение проволокой, автоматическое соединение лентой и соединение с помощью флип-чипа. Несмотря на то, что TAB и FC обладают хорошими электрическими характеристиками, они в основном используются для микросхем с небольшим количеством операций ввода-вывода или с особыми требованиями из-за высокой стоимости оборудования. В отличие от этого, WB занимает лидирующие позиции в области электрических соединений микросхем, особенно для компоновки микросхем в 3D-упаковке.

Электрическое соединение микросхемы (упаковка нулевого уровня)

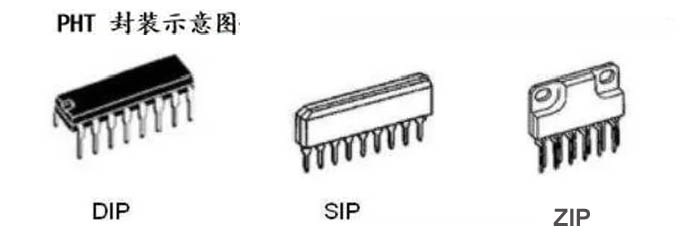

Упаковка с контактной резьбой (PTH) - это традиционная форма упаковки, в которой используются переходные отверстия для соединения матрицы с целевой платой. К этому типу упаковки относится классическая DIP-упаковка. Ранние интегральные схемы обычно выбирали такую форму упаковки из-за небольшого количества контактов. К производным от DIP-упаковок относятся пакеты SIP и ZIP, которые имеют улучшенное расположение штифтов и улучшенную форму для адаптации к различным областям применения.

DIP,SIP,ZIP package

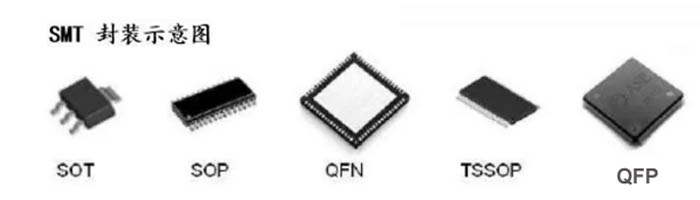

3.2 Технология поверхностного монтажа (SMT)

Это современная технология упаковки, которая занимает меньше места при проектировании печатных плат, чем традиционная упаковка PTH. Распространенные комплекты для поверхностного монтажа включают в себя небольшие пластиковые транзисторы (SOT), компактную упаковку с контуром (SOP), четырехслойную упаковку без выводов (QFN), тонкую упаковку с контуром (TSSOP), четырехслойную упаковку (QFP) и четырехслойную упаковку без выводов. Упаковка для чипов (QFN) и т.д. Количество штифтов и расстояние между ними, поддерживаемые этими формами упаковки, постепенно увеличиваются, что приводит к уменьшению размера упаковки чипов и увеличению плотности штифтов. Основными преимуществами упаковки для поверхностного монтажа являются небольшие размеры и высокая плотность контактов. Она подходит для многослойного монтажа и может значительно повысить плотность монтажа и эффективность использования печатных плат.

SMT Package

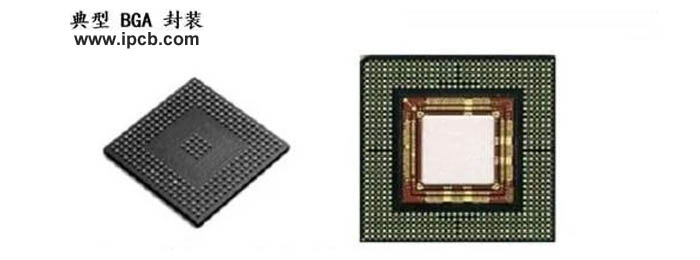

В корпусе BGA используются шариковые контакты, расположенные в нижней части корпуса, что отвечает потребностям микросхем высокой плотности и небольшого размера. Его преимущества заключаются в низкой частоте отказов, небольшом размере упаковки, отличной копланарности выводов, исключающей деформацию выводов, снижении влияния сопротивления /емкости / индуктивности, улучшении теплоотдачи и высокой плотности упаковки. Это одна из основных форм упаковки современных крупномасштабных интегральных схем.

Пакет BGA

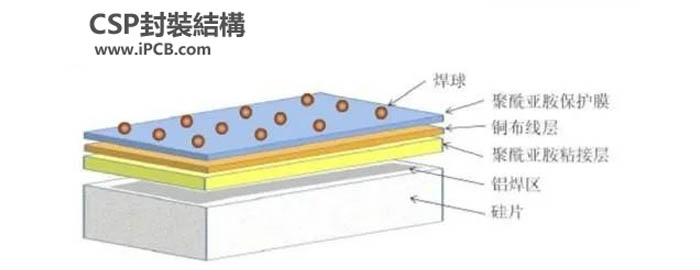

3. Технология CSP (wafer level packaging) обеспечивает высокую производительность и высокие требования к надежности за счет упаковки чипа в чрезвычайно компактную упаковку, близкую по размеру к чистому чипу, при минимальном размере упаковки. Он поддерживает конфигурацию из более чем 2000 контактов и обладает отличной теплопроводностью и оптимизацией расстояния прохождения сигнала, адаптируясь к потребностям современных высокочастотных чипов памяти.

Структура упаковки CSP

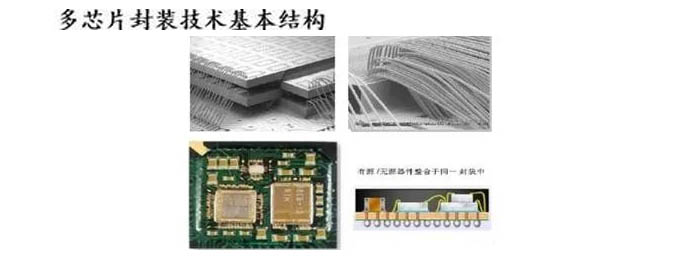

4. Технология многослойной упаковки использует механические и электрические методы сборки для экспоненциального увеличения объема памяти или реализации многофункциональных электронных конструкций в ограниченном пространстве, решая проблему ограниченного пространства и взаимосвязей. Она делится на два типа: индивидуальная упаковка и стандартная коммерческая упаковка. Первый из них более дорогой, но позволяет выполнять процессы с высокой плотностью слоев, в то время как второй имеет несколько меньшую стоимость и обычно используется для упаковки чипов в пакеты для повышения производительности модулей памяти.

Структура упаковки с несколькими чипами

4.1 Технология упаковки в стопки в основном использует укладку пластин в стопку для достижения высокой степени интеграции и экономии места. В частности, при PoP-укладке (упаковка в упаковку) используются полностью протестированные и упакованные пластины, преимущество которых заключается в высоком выходе и в том, что каждое устройство может быть протестировано индивидуально перед сборкой; в то время как при PiP-укладке (упаковка в упаковке) используются пакеты модулей для простого тестирования и низкой стоимости. ниже. Технология 3D-упаковки еще больше повышает плотность и эффективность упаковки, позволяя укладывать несколько чипов или многослойную упаковку в меньшем объеме.

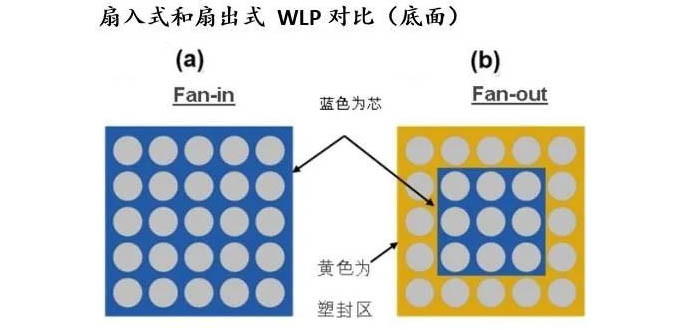

4.2 Упаковка на уровне вафель (WLP) - это технология, при которой большинство операций в процессе упаковки выполняются на вафле. Существует два основных типа упаковки: "веерная" и "раскладная".

4.3 Встраиваемый WLP упаковывается, когда пластина не разрезана. Размер устройства совпадает с размером матрицы для пластины, что подходит для приложений с низким количеством операций ввода-вывода и меньшими размерами.

4.4 Разветвление WLP делится на два процесса: сначала формуют пластины, а затем формуют их в последнюю очередь. Сначала устанавливается микросхема, а затем выполняется подключение, которое обычно используется для повышения коэффициента использования микросхемы; в то время как микросхема устанавливается позже, сначала выполняется подключение, а затем устанавливается микросхема, что является более сложным процессом, но помогает повысить коэффициент полезного действия.

Эти технологии предназначены для уменьшения размеров упаковки, снижения затрат и повышения производительности. Они являются одной из ключевых технологий для современных высокоинтегрированных электронных продуктов.

Два типа процессов WLP

Два типа процессов WLP - SIP (система в упаковке) и SoP (Система на упаковке) - это технологии упаковки, которые быстро развиваются в последние годы и особенно подходят для бытовой электроники и продуктов мобильной связи. Отличающиеся высокой плотностью, низким энергопотреблением, миниатюризацией, гетерогенной интеграцией и низкой стоимостью, они стали важным технологическим решением для достижения высокопроизводительной системной интеграции. Упаковка SiP/SoP имеет широкий спектр рынков применения и перспектив развития в области микроэлектроники и является одним из основных технологических решений, которое в будущем превзойдет закон Мура.

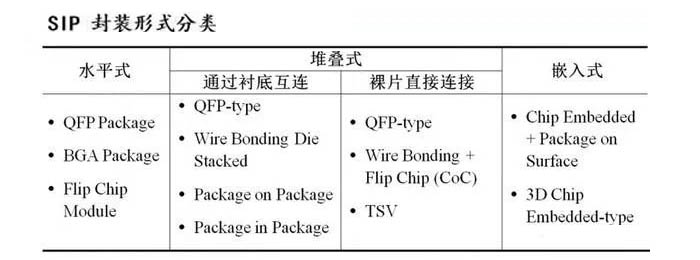

Классификация инкапсуляции SIP

Многокристальная компонентная упаковка (MCM) - ключевая технология для упаковки на системном уровне. Две или более микросхем соединяются между собой с помощью подложки, образуя полноценную функциональную упаковку. Эта технология эффективно решает проблемы, связанные с возрастающей функциональной сложностью чипа, и может обеспечить миниатюризацию продукта и высокие требования к производительности.

Выше мы рассказали о состоянии отрасли и развитии производства подложек для упаковки транзисторов. Для получения дополнительной информации о подложках для упаковки транзисторов, пожалуйста, перейдите по ссылке: разделы упаковки микросхем.